설계 일정 및 단가

| ARTWORK |

| 타입 |

PIN 단가 |

| MLB |

₩ 1,100 |

| Build up |

₩ 1,400 |

※ REMARK : 수정설계 관련

1) 하루 4H 이내 수정 설계 : 무상처리 (PCB,SMT 진행시)

2) 수정설계비 : ₩200,000 (8H 기준)

3) 기본설계비 : ₩300,000 (300PIN 이하)

| Layer |

Pin수 |

Pin Pitch(mm) |

PCB공법 |

Artwork 일정 |

| 2 |

200-400 |

QFP-0.5p |

일반 |

2~3 days |

| 4 |

400-700 |

0.5 ~ 0.8p |

일반 |

3~4 days |

| 6 |

800-1,000 |

0.5 ~ 0.8p |

일반 |

4~5 days |

| 8 |

1,500-2,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

6~7 days |

| 8 |

3,000-3,500 |

FBGA 0.4~0.8p |

일반 및 Build-up |

7~8 days |

| 8 |

3,000-4,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

8~12 days |

| 8 |

4,500-5,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

10~14 days |

| 10 |

4,500-5,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

10~14 days |

| 10 |

5,000-7,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

10~14 days |

| 10 |

7,000-9,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

12~16 days |

| 10 |

9,000-11,000 |

FBGA 0.4~0.8p |

일반 및 Build-up |

14~18 days |

| 10 |

10,000-12,000 |

QFP, BGA-0.5p |

일반 |

14~18 days |

| 12~14 |

12,000 초과 |

QFP, BGA-0.5p |

일반 |

18~24 days |

설계 이력

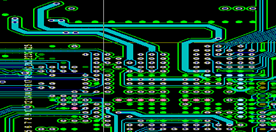

전송장비

FLC, 2.5G, 10G, MSPP, PON, DWDM의 광부/공통부/채널부 및 Backplane

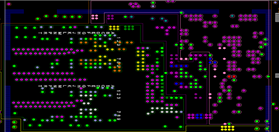

반도체 관련

IC/TEST 장비, Burning B/D, Probe Card, SDRAM Module, AP칩(ROCKCHIP-RK시리즈, Xilinx-Zynq, SONY-IMX시리즈, 텔리칩스-TCC시리즈), SDRAM+LPDDR SDRAM/DDR5

산업용 관련

초음파진단기, 의료기기, 자동차전장, ITS, CCTV, MOTOR CLUSTER, 전기식 감지 (electrical sensing board), 산업용프린트 및 복합기 제어기술(신도리코), DOOR 카메라보드, 온도센서

멀티미디어

Set top box, WALLPAD, LCD, DVR, PVR, Navi, IP set top box, Umpc, Auto-pc, Black-Box, LED

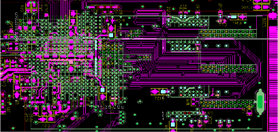

PC 관련

Tablet PC, Note PC, PC용 Mother B/D, PDA, Auto PC, Server CPU B/D, PCI Express

방산 관련

RADER, PAMA, DAMA, Compact PCI&SCSI B/D, HDT, VME

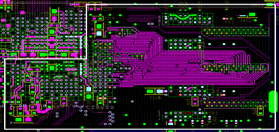

네트워크 장비

Gigabit Switch, Edge Router, NGN, Gateways, VOIP, Wireless LAN, VPN, Home-N/W, MPLS, G(E)-PON, Fire-wall, L4 Switch

기타

ASIC, SOC 개발용 FPGA B/D, VME, 제어기, SCADA, NMS등 제어 시스템, SOM(SYSTEM ON MODULE), SIB(SWITCH IN THE BASE), SCB(SENSOR CONTROL BOARD), RF(Rigid Flexible)

개선 성공 사례

| 유형 |

적용 예시 |

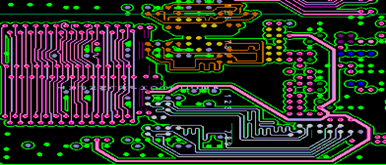

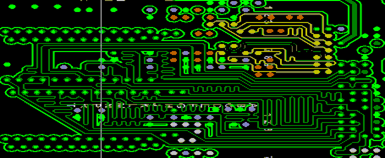

메모리 작업시

유의 사항

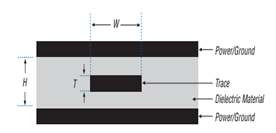

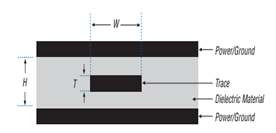

▶임피던스 매칭

(DATA 신호 50옴,

CLK 디퍼런셜

100옴 매칭)

▶DATA 신호 길이 맞춤

|

|

| 유형 | 안좋은 예 | 개선 방향 | 개선 내용 |

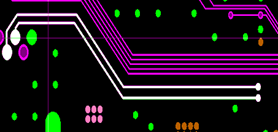

| USB 3.0,4.0 유의사항 |

|

배선 작업시 Differential Pair 형태로 작업 ,임피던스 90옴 매칭 |

|

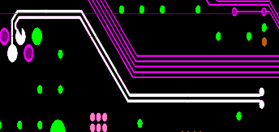

CPU 전원노이즈

개선 방법 |

|

개선 사진처럼 패턴으로 전원 연결이 아닌 내층에 PLANE 형태로 작업시 전원 노이즈 감소됨 |

|

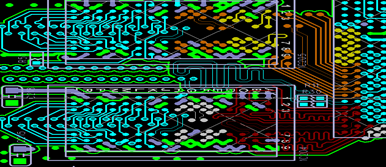

| 메모리 노이즈 개선 방법 |

|

DDR 신호가 지나가는 부분 내층에 GROUND PLANE으로 감싸면 전압 편차가 사라지는 효과를 얻을 수 있다. |

|

| CLK 신호 처리 |

|

주파수가 높은 CLK 신호를 위 아래 GROUND PLANE을 감싸서 작업시 NOISE를 감소시키는 효과를 얻을 수 있다. |

|